设计,我们可以采用合适的拓扑结构简化设计时的板级关联性。 飞思卡尔强烈推荐系统 / 板级工程师在 PCB 制板前进行设计验证,包括信号完整性、时 序等等。 1 设计检查表 如

针对DDR2-800和DDR3的PCB信号完整性设计

452x500 - 236KB - JPEG

针对DDR2-800和DDR3的PCB信号完整性设计

439x500 - 256KB - JPEG

Altium 4片DDR3 T点拓扑高速PCB设计速成实

751x428 - 147KB - JPEG

大板PCB设计 影驰DDR3版GT220破400元-影

500x332 - 167KB - JPEG

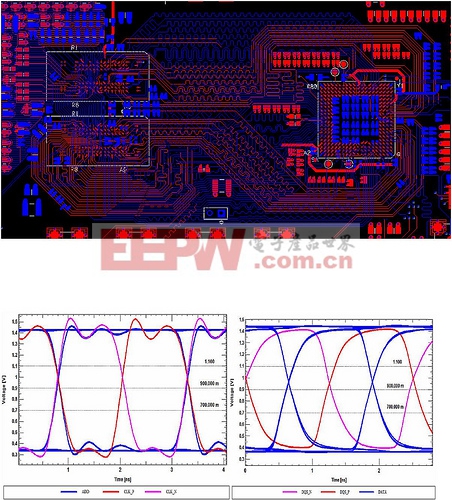

DDR3内存的PCB仿真与设计 - PCB制造相关

500x249 - 21KB - JPEG

DDR3 SDRAM 的硬件及PCB设计与要点分析(

807x582 - 111KB - JPEG

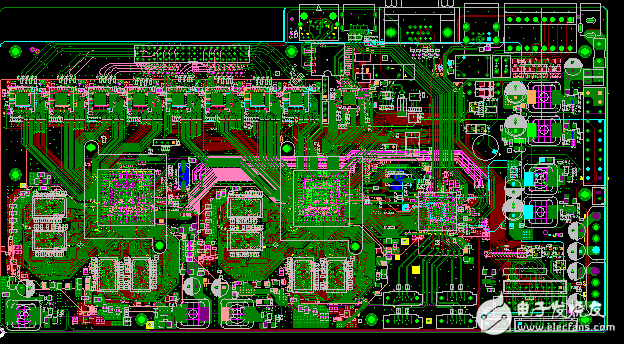

智源8210-32路 3个BGA 8个DDR3(设计PCB图

624x344 - 86KB - PNG

1600Mbps DDR3 高速信号仿真和PCB设计 - 荷

966x715 - 50KB - PNG

Cadence 6层板DDR3 PCB layout设计视频下载

1284x618 - 100KB - JPEG

针对DDR2-800和DDR3的PCB信号完整性设计

991x356 - 89KB - JPEG

DDR3 fly-by拓扑设计_Pcb_Design

690x573 - 136KB - JPEG

DDR3 SDRAM 的硬件及PCB设计与要点分析(

308x453 - 35KB - JPEG

针对DDR2-800和DDR3的PCB信号完整性设计

800x500 - 66KB - JPEG

黑色PCB设计 微星DDR3版G41主板499元_硬

500x375 - 90KB - JPEG

六层PCB底板设计 金邦白金2GB DDR3内存条

550x413 - 35KB - JPEG