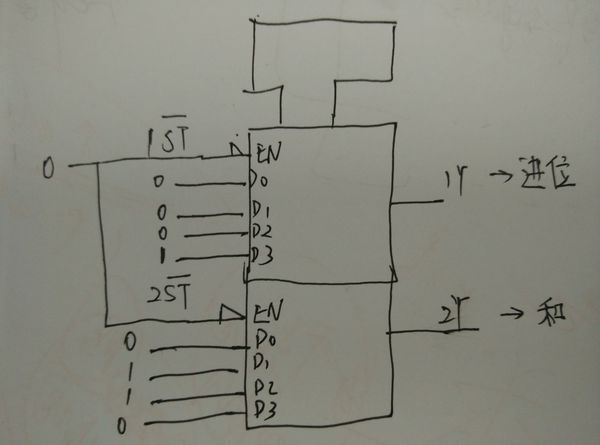

输入用A B CI输出用两个指示灯代表CO、S1写出设计过程画出逻辑图 作业帮用户 数学 1Y为全加器的和S,2Y全加器的高位进位CO,则可令数据选择器的输入为:A1=A,A0=B,1D

74ls153_light

500x364 - 111KB - JPEG

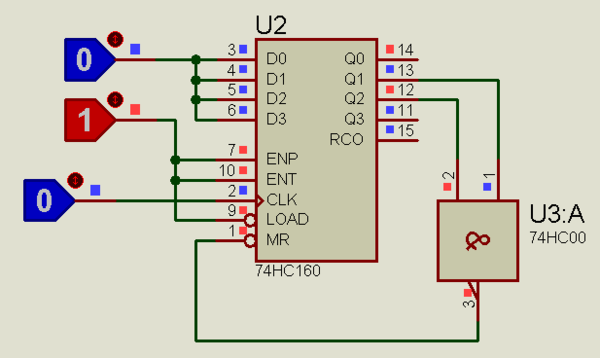

用异或门74LS86和与非门74LSOO设计实现全

473x176 - 33KB - PNG

74ls153中文资料

621x443 - 7KB - GIF

基于多数决定逻辑门的全加器电路设计

450x388 - 29KB - JPEG

全加器,全加器是什么意思-电子电路图

426x354 - 21KB - JPEG

我们可以利用组合逻辑电路设计的步骤得到全加

435x264 - 6KB - GIF

要命的组合逻辑电路设计

500x364 - 113KB - JPEG

74ls153构成表决器

500x294 - 12KB - JPEG

用4:1数据选择器实现全加器逻辑功能

425x319 - 28KB - JPEG

数字逻辑电路, 用74LS153设计监控交通信号灯

600x358 - 40KB - PNG

74ls153设计3人表决器 \/74ls153设计3人表决器

647x380 - 36KB - JPEG

试用74LS153数据选择器设计半加器

600x445 - 18KB - JPEG

怎么用双4选1数据选择器74LS153和与非门实

613x426 - 22KB - JPEG

数据选择器74LS153中文资料|TTL芯片-Dz3w.C

621x443 - 8KB - GIF

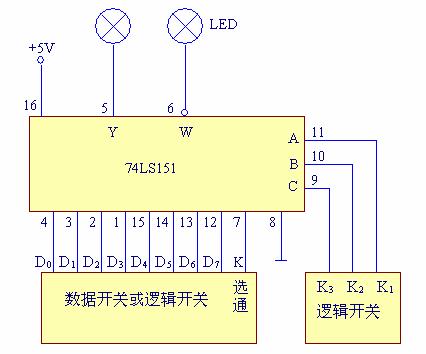

用八选一数据选择器74LS151设计一个多数表

960x720 - 27KB - JPEG