超前进位加法器延时分析– OmegaXYZ

超前进位加法器延时分析– OmegaXYZ

1370x768 - 70KB - PNG

超前进位加法器

超前进位加法器

220x220 - 32KB - PNG

超前进位加法器+

超前进位加法器+

893x472 - 147KB - PNG

超前进位加法器原理PPT

超前进位加法器原理PPT

1170x810 - 210KB - JPEG

超前进位加法器的设计

超前进位加法器的设计

657x400 - 21KB - JPEG

超前进位加法器

超前进位加法器

268x201 - 12KB - JPEG

2.超前进位加法器设计

2.超前进位加法器设计

306x358 - 40KB - PNG

2.超前进位加法器设计

2.超前进位加法器设计

788x433 - 35KB - PNG

四位超前进位加法器原理

四位超前进位加法器原理

461x339 - 11KB - PNG

四位超前进位加法器原理

四位超前进位加法器原理

881x423 - 26KB - PNG

试验二 超前进位加法器 设计

试验二 超前进位加法器 设计

658x439 - 287KB - PNG

4bits超前进位加法器全定制设计实验报告

4bits超前进位加法器全定制设计实验报告

367x326 - 0KB - PNG

超前进位加法器+_word文档在线阅读与

超前进位加法器+_word文档在线阅读与

893x500 - 134KB - PNG

超前进位加法器的设计-学位论文.doc

超前进位加法器的设计-学位论文.doc

993x1404 - 51KB - PNG

HDL语言编写的四位超前进位加法器PPT

HDL语言编写的四位超前进位加法器PPT

1080x810 - 60KB - JPEG

简介:超前进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通全加器串联时互相进位产生

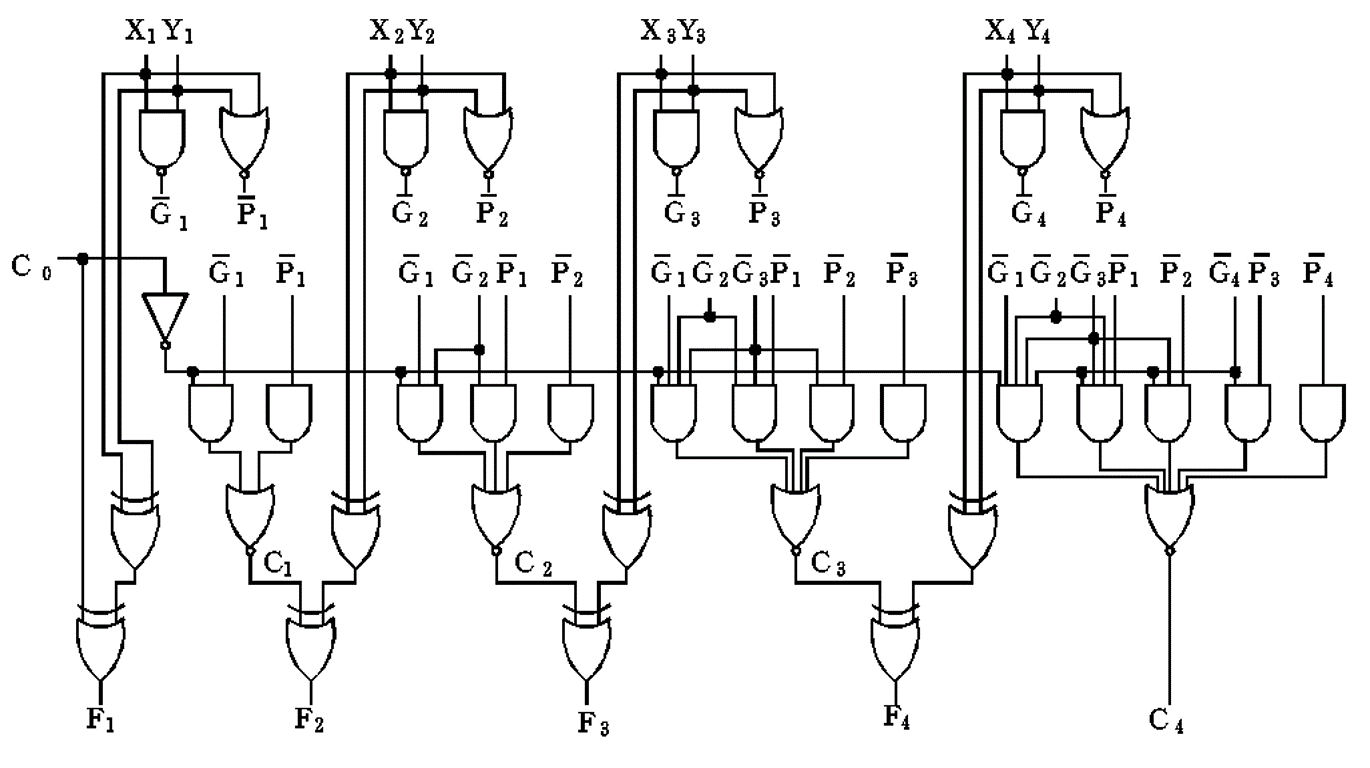

超前进位加法器原理74283为4位超前进位加法器,不同于普通串行进位加法器由低到高逐级进位,超前进位加法器所有位数的进位大多数情况下同时产生,运算速度快,电路结构复杂。其管脚如图1所示:图1 74283管脚图其真值表如下所示:表1 4位超前进位加法器真值表由全加器的真值表可得Si和Ci的逻辑表达式:定义

上述表达式显示了进位项可以从进位产生和进位传播项求得,在计算中可以通过迭代的方法实现。超前进位加法器的逻辑电路表明了每位进位项的延迟时间都是两级逻辑门的延

超前进位加法器以及LED显示 VIP专享文档 VIP专享文档是百度文库认证用户/机构上传的专业性文档,文库VIP用户或购买VIP专享文档下载特权礼包的其他会员用户可用VIP专享

数电书上说道超前进位加法器,没有仔细讲。上网搜了这篇资料,摘抄下来串行进位加法器需要一级一级的进位,进位延迟很大。先行进位加法器(也叫超前进位加法器)可以有效的

四 川 大 学 计 算 机 学 院、软 件 学 院实 验 报 告 学号:姓名: 专业: 班级: 第 周 课程名称 计算机组成原理实验课时实验项目超前进位加法器设计实验实验时间实验目的 1. 掌握超前进位加法器的原理及其设计方法。2. 熟悉CPLD应用设计及EDA软件的使用 实验环境 TD-CMA实验系统一台,PC机一台 实验内容(算法