关键词:可配置IP;VLIW;Jazz;SoC1、引言随着IC的生产成本持续上涨,消费类电子产品制造商不得不 您所在位置 FPGA_ASIC-SoC设计链中的可配置IP.pdf 7页 本文档一共被下

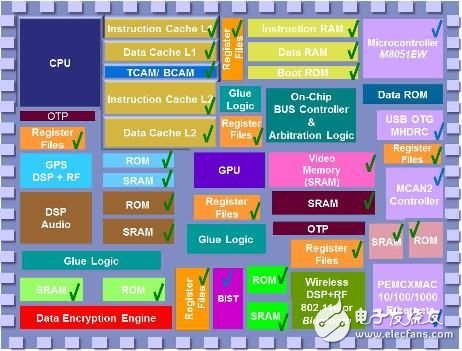

支援多cpu架构 soc fpga增强ip重用性 - 21ic中

500x487 - 39KB - JPEG

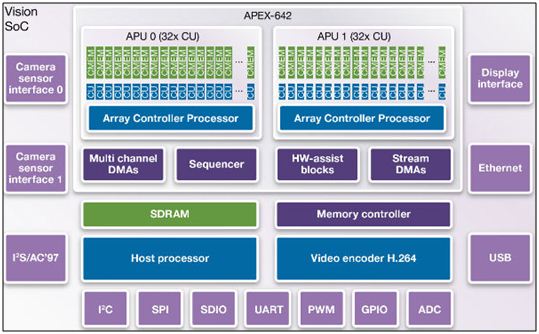

马达控制IP模块 - 基于SoC FPGA的工业和马达

583x254 - 58KB - PNG

基于FPGA的SOC外部组件控制器IP的设计 - F

254x203 - 11KB - JPEG

基于FPGA的SOC外部组件控制器IP的设计 - F

246x224 - 14KB - JPEG

Xylon推出基于Xilinx Zynq SoC的ADAS IP核 - F

538x302 - 29KB - JPEG

Xylon推出基于Xilinx Zynq SoC的ADAS IP核 - F

487x270 - 27KB - JPEG

使用教程分享连载:在Zynq AP SoC设计中高效

600x338 - 35KB - JPEG

为ASIC和SoC设计实现最佳化嵌入式存储器 -

462x351 - 47KB - JPEG

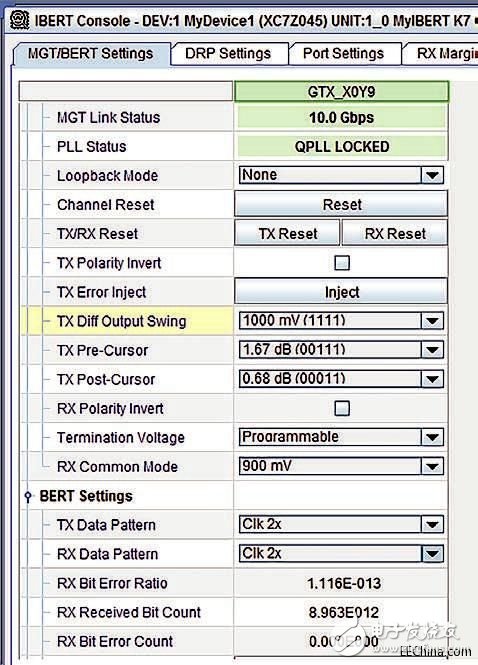

演示ASIC IP性能与质量需要有FPGA中立的设

539x334 - 39KB - JPEG

如何使用Zynq SoC和赛灵思IP核简化高速光学

478x665 - 88KB - JPEG

FPGA设计服务,数字ASIC设计服务,SOC IP 设

180x180 - 8KB - JPEG

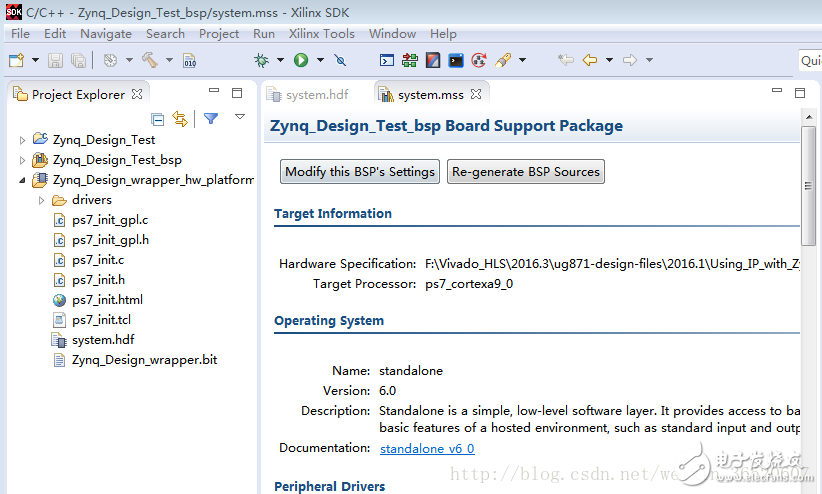

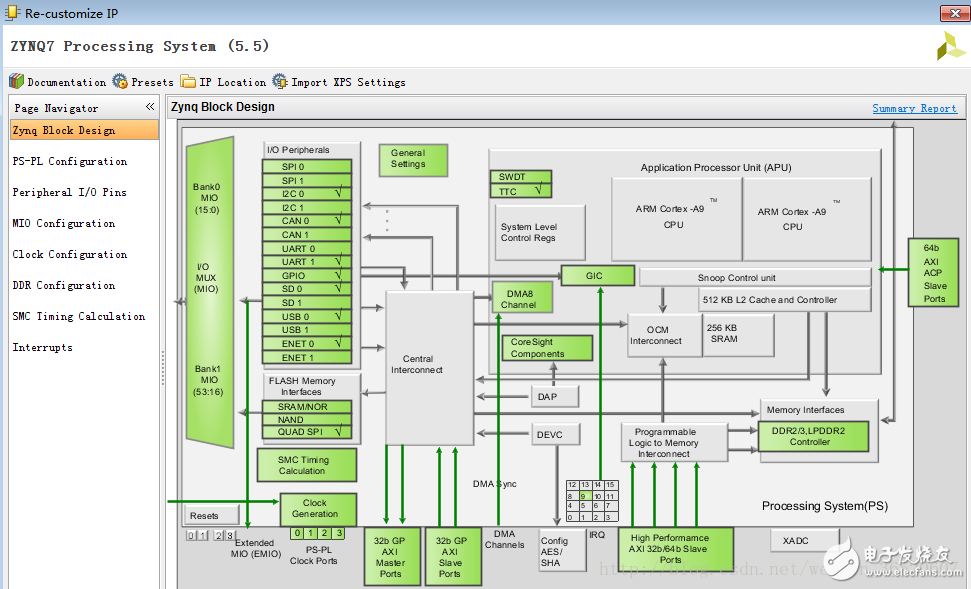

使用教程分享:在Zynq AP SoC设计中高效使用

822x494 - 61KB - PNG

使用教程分享:在Zynq AP SoC设计中高效使用

971x589 - 121KB - PNG

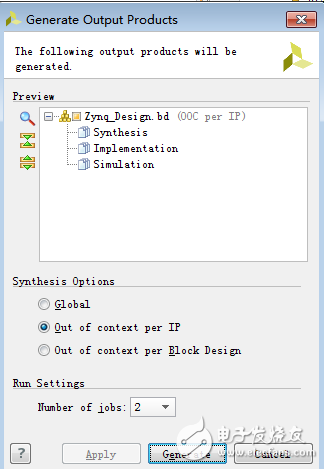

使用教程分享:在Zynq AP SoC设计中高效使用

1128x385 - 62KB - PNG

使用教程分享:在Zynq AP SoC设计中高效使用

324x469 - 24KB - PNG