莱迪思半导体公司(NASDAQ: LSCC),客制化智能互连解决方案市场的领先供应商,今日宣布推出7款全新的模块化IP核,支持屡获殊荣的CrossLink FPGA产品系列,可为消费电子

引入Cortex-M3技术 XMOS推xCORE-XA多核微

550x253 - 97KB - JPEG

IC设计技术中的IP核互连- IC 设计,IP 核,SoC - 技

397x260 - 15KB - JPEG

IP核

176x200 - 7KB - JPEG

使用LabVIEW FPGA模块设计IP核

332x312 - 6KB - GIF

基于Avalon-ST接口帧读取的IP核设计应用研究

355x254 - 15KB - GIF

基于SoPC的二维IDCT分布式算法的IP核研究-

396x200 - 25KB - GIF

soc技术支撑之ip核_产品创新数字化(plm)_eda

428x292 - 20KB - JPEG

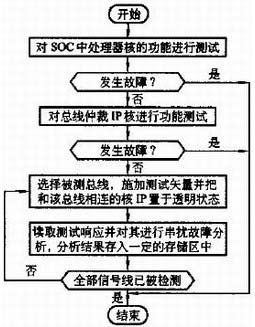

基于SOC中处理器核的串扰故障激励检测

255x327 - 20KB - JPEG

Xilinx发布新一代IP视频连接解决方案满足新兴

600x338 - 24KB - JPEG

《SoC设计与IP核重用技术》(马光胜,冯刚)

280x280 - 21KB - JPEG

如何为SoC设计选择IP核_电子资料技术文库_电

400x187 - 29KB - JPEG

基于DDS IP核及Nios II的可重构信号源设计

450x243 - 80KB - JPEG

基于Avalon总线的可配置LCD控制器IP核的设计

514x254 - 42KB - JPEG

vivado设计三:一步一步生成自己的自定义IP核-

458x354 - 37KB - JPEG

SoC设计与IP核重用技术 马光胜 国防工业出版

500x500 - 34KB - JPEG