链路接口需要进行串并转换,这种串并转换将产生较大的延时。除此之外 PCIe 总线的数据 报文需要经过事务层、 数据链路层和物理层, 这些数据报文在穿越这些层次时, 也将带

\/信号处理中的基于双缓冲与单缓冲比较总线设

500x208 - 29KB - JPEG

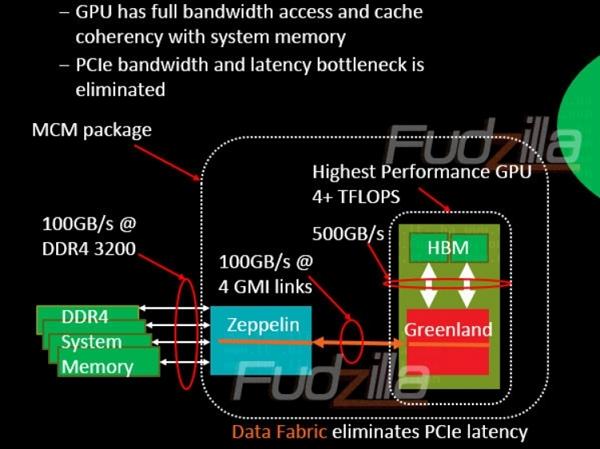

AMD全新总线曝光:带宽 延迟完爆PCI-E_CPU

600x449 - 41KB - JPEG

AMD全新总线曝光:带宽、延迟完爆PCI-E-AMD

600x449 - 134KB - JPEG

基于Virtex-6 FPGA的双缓冲模式PCIe总线设计

500x208 - 83KB - JPEG

AMD全新总线曝光:带宽、延迟完爆PCI-E - 集微

600x449 - 32KB - JPEG

AMD全新总线曝光:带宽、延迟完爆PCI-E - 集微

400x215 - 17KB - JPEG

基于Virtex-6 FPGA的双缓冲模式PCIe总线设计

500x208 - 34KB - GIF

基于Virtex-6 FPGA的双缓冲模式PCIe总线设计

500x208 - 54KB - GIF

基于Virtex-6 FPGA的双缓冲模式PCIe总线设计

500x208 - 32KB - GIF

基于Virtex-6 FPGA的双缓冲模式PCIe总线设计

500x208 - 54KB - GIF

基于FPGA的双缓冲模式PCI Express总线设计

500x208 - 51KB - GIF

ORICO推出PCI-E M.2 SSD磁盘阵列卡,10Gbp

820x681 - 192KB - PNG

基于PCIe总线的显微镜图像采集系统设计

320x236 - 43KB - JPEG

基于双缓冲与单缓冲比较总线设计方案(2)-可编

478x223 - 21KB - JPEG

HyperX首款PCIe固态硬盘即将上市_硬件资讯_

700x466 - 55KB - JPEG