虽然多家厂商已透过TSV成功开发3D IC,并改善诸多问题,但TSV仍面临到高成本的课题,有鉴于此,Veeco改变过去利用CMP与干式蚀刻的方式,而采用湿式蚀刻制程来达成TSV。

湿蚀刻制程降低TSV成本 更易实现3D IC

299x245 - 7KB - JPEG

中微推出用于3DIC及封装的TSV蚀刻设备 - 集微

400x300 - 15KB - JPEG

美国应用材料公司光掩膜与TSV蚀刻部首席技术

720x576 - 1620KB - BMP

台积电举办技术研讨会,介绍TSV及蚀刻的最新

230x218 - 8KB - JPEG

3D集成系统的测试挑战 - 工控设备

542x315 - 33KB - JPEG

中微推出用于3DIC及封装的TSV蚀刻设备 - 集微

250x166 - 7KB - JPEG

半导体科技.先进封装与测试杂志 - TSV制程技术

720x540 - 59KB - JPEG

3D IC-TSV技术与可靠性研究-AET-电子技术应

443x283 - 34KB - GIF

WCSP 在克服各种挑战的同时不断发展_老古网

400x310 - 28KB - JPEG

美国泛林推出用于3维LSI TSV的300mm晶圆蚀

170x172 - 36KB - JPEG

盛美Ultra C SAPS兆声波单片清洗设备将亮相2

499x496 - 23KB - JPEG

TSV制程技术整合分析

300x225 - 13KB - JPEG

自动化技术助力克服晶圆级封装生产效率挑战_

500x282 - 25KB - JPEG

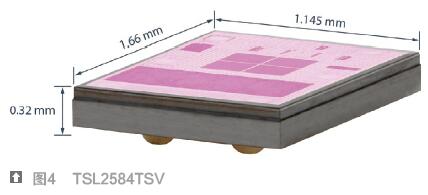

满足穿戴式产品对于超小型环境光传感器的需求

428x195 - 9KB - JPEG

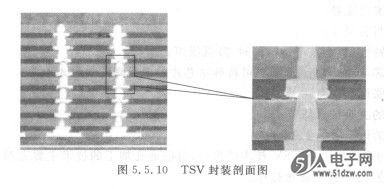

TSV技术-技术资料-51电子网

384x189 - 13KB - JPEG