微MICROPROCESSORS处理机高阻衬底CMOS外延工艺研究刘旸,唐冬,孔明(中国电子科技集团公司第四十七研究所,沈阳11003)摘要:针对于高阻衬底、高阻外延工艺与常规C

硕士论文-固相外延COSI2薄膜技术在深亚微米

993x1404 - 43KB - PNG

N阱CMOS工艺流程-经典.ppt

1152x864 - 937KB - PNG

CMOS集成电路工艺流程解说.pptx

1152x864 - 271KB - PNG

两微米外延N阱CMOS艺的研究

109x154 - 10KB - JPEG

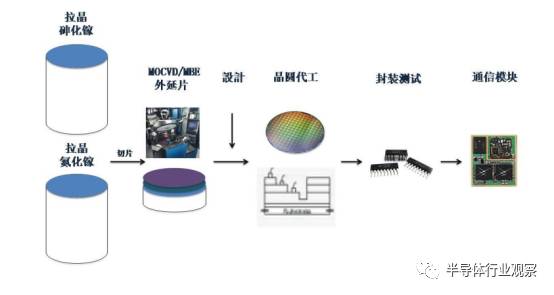

芯片制造主要有五大步骤_国内硅片制造商迎来

517x322 - 6KB - JPEG

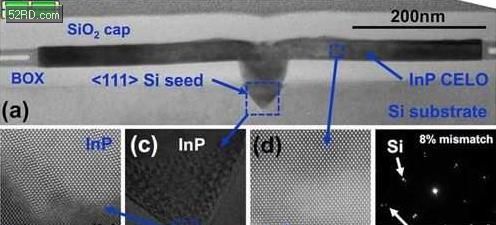

欧盟为5G打造III-V族CMOS技术

500x255 - 28KB - JPEG

[转载]CMOS版图分析_stm2010

576x418 - 108KB - JPEG

超越7nm!欧盟启动5G芯片CMOS工艺研究 - 国

500x255 - 38KB - JPEG

欧盟为5G打造III-V族CMOS技术 - 集微网:老杳微

500x255 - 20KB - JPEG

欧盟为5G打造III-V族CMOS技术 - 我爱研发网 5

496x225 - 25KB - JPEG

浅析低成本CMOS图像传感器对医学技术发展前

392x203 - 17KB - JPEG

基于0.5μm CMOS工艺的新型BiCMOS集成运

400x155 - 14KB - JPEG

欧盟为5G打造III-V族CMOS技术_IC供应链_供应

500x220 - 12KB - JPEG

1.1 集成电路发展史简介_CMOS集成电路后端

353x248 - 68KB - PNG

解读射频前端及全球格局,5G必争之地

554x295 - 12KB - JPEG