一种集成电路后段铜互连工艺中降低通孔间介质材料的K值的方法,采用一表面具有阻挡层的半导体衬底,并在所述半导体衬底上设定通孔区域,其特征在于,包括:步骤01:在所述阻

![铜互连工艺[半导体]_老古开发网文章](http://www.laogu.com/news/upload/img3/2683_26_1.jpg)

铜互连工艺[半导体]_老古开发网文章

350x216 - 46KB - JPEG

半导体集成电路铜组合物工艺资料,半导体集成

400x400 - 15KB - JPEG

半导体电镀中45nm铜工艺面临的挑战-全球机械

332x400 - 28KB - JPEG

铜半导体沉淀方法工艺资料,铜半导体的制作方

300x300 - 17KB - JPEG

在半导体器件中实施铜连线的空隙工艺方法

320x487 - 19KB - JPEG

半导体后段工艺中布线技术的革命:基于铜的金

200x132 - 15KB - GIF

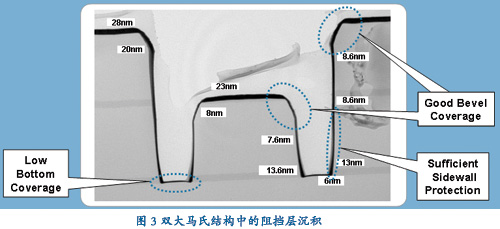

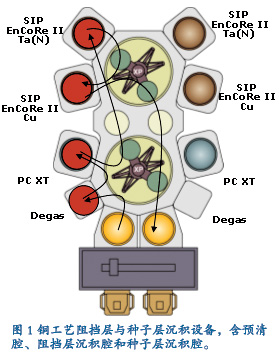

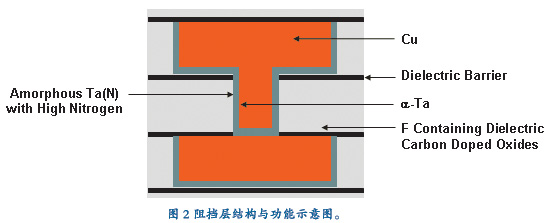

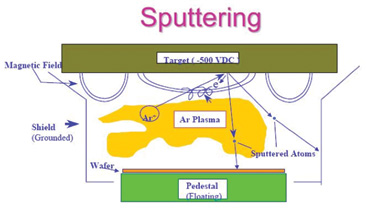

铜制程阻挡层\/种子层沉积工艺的最新进展[半导

500x229 - 40KB - JPEG

半导体引线键合工艺过程中的脱焊问题研究.pd

800x1131 - 209KB - PNG

安森美半导体推出HighQ硅-铜集成无源器件制

1102x661 - 79KB - PNG

铜制程阻挡层\/种子层沉积工艺的最新进展[半导

279x353 - 45KB - JPEG

铜制程阻挡层\/种子层沉积工艺的最新进展[半导

549x223 - 23KB - JPEG

半导体致冷元件工艺流程图

443x552 - 27KB - JPEG

半导体后段工艺中布线技术的革新-基于铝的金

367x208 - 24KB - JPEG

工艺礼品加工设备-供应凹凸模、冲头、铜工半

508x339 - 22KB - JPEG

铜CMP后的清洗工艺和填加剂在其中的作用[半

462x349 - 75KB - GIF