一种实现计时器变为倒计时器的设计方案 - 单片

354x240 - 8KB - JPEG

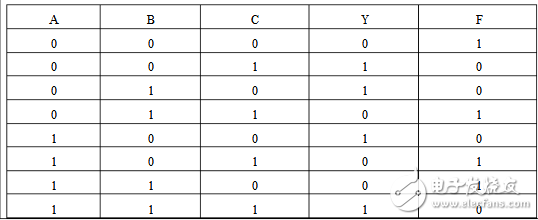

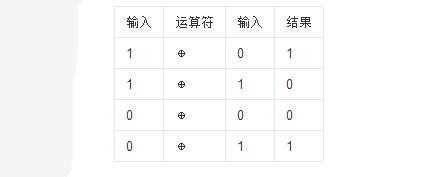

三输入异或门真值表计算详解

538x220 - 11KB - PNG

一种实现计时器变为倒计时器的设计方案_大比

354x240 - 6KB - JPEG

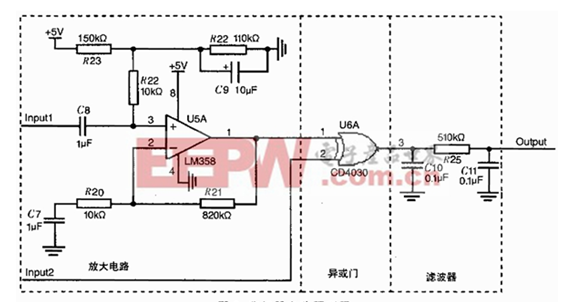

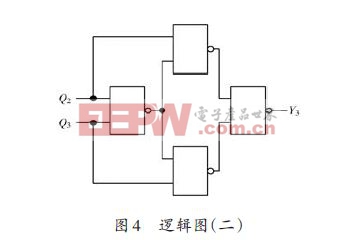

鉴相器原理

561x302 - 90KB - PNG

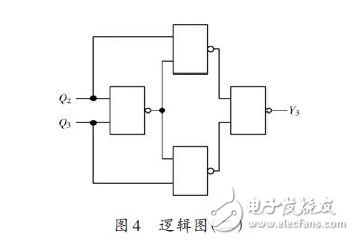

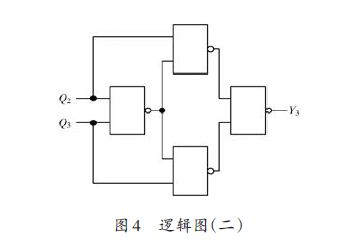

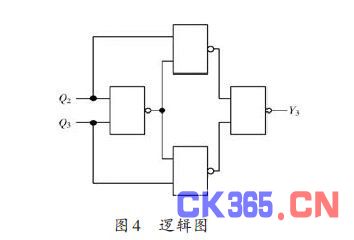

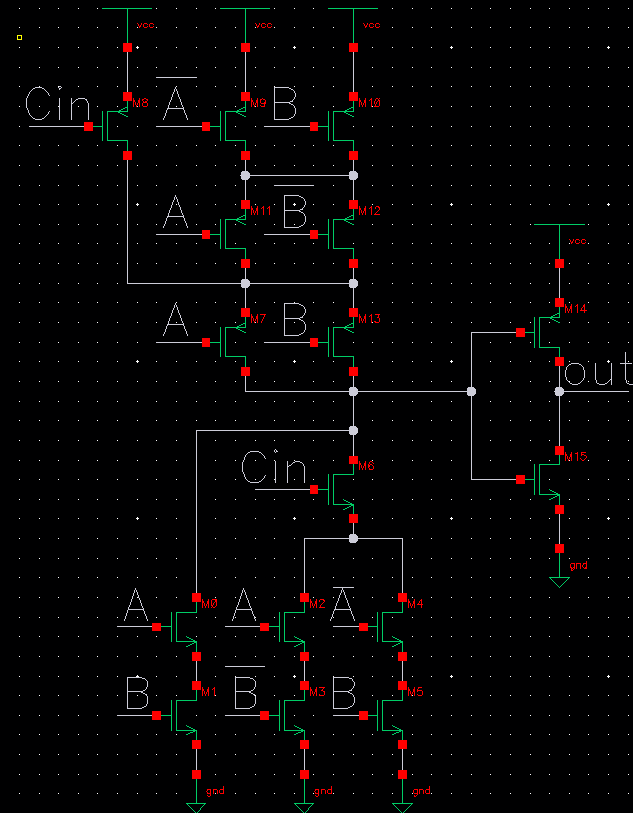

三输入异或门逻辑图及表达式解析

541x411 - 77KB - PNG

异或门的逻辑功能解析 - 电子常识 - 电子发烧友

346x291 - 18KB - JPEG

异或同或门逻辑符号_利用或门和非门设计的异

446x167 - 9KB - JPEG

一种实现计时器变为倒计时器的设计方案 测控

354x240 - 8KB - JPEG

用电路符号表示异或门的方法

429x177 - 5KB - JPEG

(第2讲)改第2章基本逻辑运算和逻辑门.ppt

141x200 - 6KB - JPEG

2数据的表示和运算-1重点.ppt

960x720 - 117KB - JPEG

2补码加法运算.ppt

141x200 - 3KB - JPEG

电路里与非门、或门,这个门从物理层怎样解读

633x813 - 19KB - PNG

一种实现计时器变为倒计时器的设计方案

354x240 - 19KB - JPEG

第13章 数字电路的基础知识.ppt

1152x864 - 79KB - PNG

表示方法布尔代数法按一定逻辑规律进行运算的代数。与普通代数不同,布尔代数中的变量是二元值的逻辑变量。

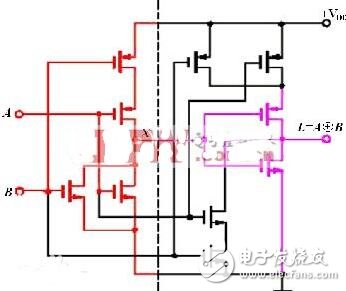

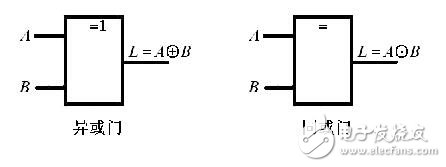

异或门(英语:Exclusive-OR gate,简称XOR gate,又称EOR gate、ExOR gate)是数字逻辑中实现逻辑异或的

异或门 的算法 事怎么样的?请教实现异或运算的门电路是异或门,异或门的真值表如表1.13所示,其逻辑符号如

本文开始对逻辑异或运算进行了介绍,介绍了逻辑异或运算性质,其次分析了逻辑异或运算该怎么算,最后介绍了

如何用与非门和异或门实现平方运算?仅对两位的二进制数,解决方案1:设两位二进制数各为A1A0,B1B0,输出为C3

展开全部 设两位二进制数各为A1A0,B1B0,输出为C3C2C1C0, 然后列真值表,分别列出C3C2C1C0的逻辑表达式,再

参加运算的两个数据,按二进制位进行“异或”运算。运算规则:0^0=0;0^1=1;1^0=1;1^1=0;即:参加运算的

异或门是什么意思虽然异或不是开关代数的基本运算之一,但是在实际运用中相当普遍地使用分立的异或门.